# Automatic Generation of Models of Microarchitectures

# Dissertation

zur Erlangung des Grades des Doktors der Ingenieurwissenschaften der Fakultät für Mathematik und Informatik der Universität des Saarlandes

> von Andreas Abel

Saarbrücken 2020 Tag des Kolloquiums: 12. Juni 2020

**Dekan:** Prof. Dr. Thomas Schuster

Prüfungsausschuss:

Vorsitzender: Prof. Dr. Thorsten Herfet

Berichterstatter: Prof. Dr. Jan Reineke

Prof. Dr. Wolfgang J. Paul

Dr. Boris Köpf

Akademischer Mitarbeiter: Dr. Roland Leißa

#### Abstract

Detailed microarchitectural models are necessary to predict, explain, or optimize the performance of software running on modern microprocessors. Building such models often requires a significant manual effort, as the documentation provided by hardware manufacturers is typically not precise enough. The goal of this thesis is to develop techniques for generating microarchitectural models automatically.

In the first part, we focus on recent x86 microarchitectures. We implement a tool to accurately evaluate small microbenchmarks using hardware performance counters. We then describe techniques to automatically generate microbenchmarks for measuring the performance of individual instructions and for characterizing cache architectures. We apply our implementations to more than a dozen different microarchitectures.

In the second part of the thesis, we study more general techniques to obtain models of hardware components. In particular, we propose the concept of gray-box learning, and we develop a learning algorithm for Mealy machines that exploits prior knowledge about the system to be learned.

Finally, we show how this algorithm can be adapted to minimize incompletely specified Mealy machines—a well-known NP-complete problem. Our implementation outperforms existing exact minimization techniques by several orders of magnitude on a number of hard benchmarks; it is even competitive with state-of-the-art heuristic approaches.

## Zusammenfassung

Zur Vorhersage, Erklärung oder Optimierung der Leistung von Software auf modernen Mikroprozessoren werden detaillierte Modelle der verwendeten Mikroarchitekturen benötigt. Das Erstellen derartiger Modelle ist oft mit einem hohen Aufwand verbunden, da die erforderlichen Informationen von den Prozessorherstellern typischerweise nicht zur Verfügung gestellt werden. Das Ziel der vorliegenden Arbeit ist es, Techniken zu entwickeln, um derartige Modelle automatisch zu erzeugen.

Im ersten Teil beschäftigen wir uns mit aktuellen x86-Mikroarchitekturen. Wir entwickeln zuerst ein Tool, das kleine Microbenchmarks mithilfe von Performance Countern auswerten kann. Danach beschreiben wir Techniken, um automatisch Microbenchmarks zu erzeugen, mit denen die Leistung einzelner Instruktionen gemessen sowie die Cache-Architektur charakterisiert werden kann.

Im zweiten Teil der Arbeit betrachten wir allgemeinere Techniken, um Hardwaremodelle zu erzeugen. Wir schlagen das Konzept des "Gray-Box Learning" vor, und wir entwickeln einen Lernalgorithmus für Mealy-Maschinen, der bekannte Informationen über das zu lernende System berücksichtigt.

Zum Abschluss zeigen wir, wie dieser Algorithmus auf das Problem der Minimierung unvollständig spezifizierter Mealy-Maschinen übertragen werden kann. Hierbei handelt es sich um ein bekanntes NP-vollständiges Problem. Unsere Implementierung ist in mehreren Benchmarks um Größenordnungen schneller als vorherige Ansätze.

## Acknowledgements

First and foremost, I would like to thank my advisor, Prof. Jan Reineke. He gave me the freedom to explore my own ideas and was always available for discussions and to provide guidance. I'm looking forward to continuing working with him!

I would also like to thank Prof. Wolfgang Paul and Dr. Boris Köpf for reviewing my thesis, and Prof. Thorsten Herfet for acting as the chair of the examination board.

Finally, I would like to thank my current and former colleagues at the Real-Time and Embedded Systems Lab and the Compiler Design Lab. In particular, I would like to thank Dr. Roland Leißa for serving as the academic assistant on my examination board.

# Contents

| 1        | Intr | roduction                                            | 13              |  |  |  |  |  |

|----------|------|------------------------------------------------------|-----------------|--|--|--|--|--|

|          | 1.1  | Contributions and Structure of This Thesis           | 14              |  |  |  |  |  |

|          | 1.2  | Publications                                         | 19              |  |  |  |  |  |

| <b>2</b> | nan  | noBench: A Low-Overhead Tool for Running Microbench- |                 |  |  |  |  |  |

| _        |      | ks on x86 Systems                                    | 21              |  |  |  |  |  |

|          | 2.1  | Introduction                                         | 21              |  |  |  |  |  |

|          | 2.2  | Background                                           | 23              |  |  |  |  |  |

|          | 2.2  | 2.2.1 Hardware Performance Counters                  | $\frac{23}{23}$ |  |  |  |  |  |

|          |      | 2.2.2 Assembler Instructions                         | $\frac{25}{25}$ |  |  |  |  |  |

|          | 2.3  | Features                                             | $\frac{25}{25}$ |  |  |  |  |  |

|          | 2.0  | 2.3.1 Example                                        | $\frac{26}{26}$ |  |  |  |  |  |

|          |      | 2.3.2 Generated Code                                 | $\frac{20}{27}$ |  |  |  |  |  |

|          |      | 2.3.3 Running the Generated Code                     | $\frac{27}{27}$ |  |  |  |  |  |

|          |      |                                                      | 29              |  |  |  |  |  |

|          |      | 2.3.4 Kernel/User Mode                               | 29              |  |  |  |  |  |

|          |      |                                                      | 29              |  |  |  |  |  |

|          |      | 1                                                    | 30              |  |  |  |  |  |

|          |      | 2.3.7 Accessing Memory                               | $\frac{30}{30}$ |  |  |  |  |  |

|          |      | <u> </u>                                             |                 |  |  |  |  |  |

|          |      |                                                      | 30              |  |  |  |  |  |

|          |      | 2.3.10 Performance Counter Configurations            | 31              |  |  |  |  |  |

|          |      | 2.3.11 Execution Time of nanoBench                   | 31              |  |  |  |  |  |

|          | 2.4  | 2.3.12 Supported Platforms                           | 32              |  |  |  |  |  |

|          | 2.4  | Implementation                                       | 32              |  |  |  |  |  |

|          |      | 2.4.1 Accurate Performance Counter Measurements      | 32              |  |  |  |  |  |

|          |      | 2.4.2 Generating Code                                | 33              |  |  |  |  |  |

|          |      | 2.4.3 Kernel Module                                  | 34              |  |  |  |  |  |

|          |      | 2.4.4 Allocating Physically-Contiguous Memory        | 34              |  |  |  |  |  |

|          | 2.5  | Related Work                                         | 35              |  |  |  |  |  |

|          | 2.6  | Conclusions and Future Work                          | 36              |  |  |  |  |  |

| 3        | uop  | s.info: Characterizing the Latency, Throughput, and  |                 |  |  |  |  |  |

|          |      | t Usage of Instructions on x86 Microarchitectures    | 39              |  |  |  |  |  |

|          | 3.1  | Introduction                                         | 40              |  |  |  |  |  |

|          | 3.2  | Related Work                                         | 42              |  |  |  |  |  |

|          | ~    | 3.2.1 Information Provided by the Manufacturers      | 42              |  |  |  |  |  |

|          |      | 3.2.2 Measurement-Based Approaches                   | 43              |  |  |  |  |  |

|          | 3.3  | Background                                           | 44              |  |  |  |  |  |

|          | 5.5  | 240119104114                                         | 1.3             |  |  |  |  |  |

# **CONTENTS**

|   |     | 3.3.1   | Pipeline of Intel Core CPUs                |

|---|-----|---------|--------------------------------------------|

|   |     | 3.3.2   | Pipeline of AMD Ryzen CPUs                 |

|   | 3.4 | Defini  | tions                                      |

|   |     | 3.4.1   | Latency                                    |

|   |     | 3.4.2   | Throughput                                 |

|   |     | 3.4.3   | Port Usage                                 |

|   | 3.5 | Algori  | $ithms \dots $ 49                          |

|   |     | 3.5.1   | Port Usage                                 |

|   |     | 3.5.2   | Latency                                    |

|   |     | 3.5.3   | Throughput                                 |

|   | 3.6 | Imple   | mentation                                  |

|   |     | 3.6.1   | Details of the x86 Instruction Set 61      |

|   |     | 3.6.2   | Measurements on the Hardware 62            |

|   |     | 3.6.3   | Analysis Using IACA 63                     |

|   |     | 3.6.4   | Machine-Readable Output 63                 |

|   | 3.7 | Evalua  | ation                                      |

|   |     | 3.7.1   | Experimental Setup                         |

|   |     | 3.7.2   | Hardware Measurements vs. Documentation 64 |

|   |     | 3.7.3   | Hardware Measurements vs. IACA 67          |

|   |     | 3.7.4   | Interesting Results                        |

|   | 3.8 | Limita  | ations                                     |

|   | 3.9 | Concl   | usions and Future Work                     |

| 4 | Cha | ractor  | rizing Cache Architectures 79              |

| _ | 4.1 |         | luction                                    |

|   | 4.2 |         | round                                      |

|   | 1.2 | _       | Cache Organization                         |

|   |     | 4.2.2   | Replacement Policies                       |

|   | 4.3 |         | -Characterization Tools                    |

|   | 1.0 | 4.3.1   | CacheInfo                                  |

|   |     | 4.3.2   | CacheSeq                                   |

|   |     | 4.3.3   | Replacement Policies                       |

|   |     | 4.3.4   | Age Graphs                                 |

|   |     | 4.3.5   | Test for Adaptive Policies                 |

|   | 4.4 |         | ts                                         |

|   | 1.1 | 4.4.1   | L1 Data Caches                             |

|   |     | 4.4.2   | L2 Caches                                  |

|   |     | 4.4.3   | L3 Caches                                  |

|   |     | 4.4.4   | Resetting the Replacement Policy State 109 |

|   |     | 4.4.5   | Implementation Costs                       |

|   | 4.5 | _       | ed Work                                    |

|   | 1.0 | 1001000 | /vx                                        |

# **CONTENTS**

|   |     | 4.5.1  | Microbenchmark-Based Cache Analysis                | . 111 |

|---|-----|--------|----------------------------------------------------|-------|

|   |     | 4.5.2  | Influence of the Replacement Policy on Performance | 440   |

|   |     |        | Prediction Accuracy                                |       |

|   |     | 4.5.3  | Security Aspects of Replacement Policies           |       |

|   | 4.6 | Concl  | usions and Future Work                             | . 115 |

| 5 |     | -      | Learning of Serial Compositions of Mealy           |       |

|   | Mac | chines |                                                    | 117   |

|   | 5.1 |        | luction                                            |       |

|   | 5.2 | Proble | em Statement                                       |       |

|   |     | 5.2.1  | Basic Notions                                      |       |

|   |     | 5.2.2  | The Gray-Box Learning Problem                      | . 120 |

|   | 5.3 | Prelin | ninaries                                           | . 121 |

|   | 5.4 | Appro  | oach                                               | . 122 |

|   |     | 5.4.1  | Observation Tables                                 | . 123 |

|   |     | 5.4.2  | Inference Algorithm                                | . 126 |

|   | 5.5 | Imple  | mentation                                          | . 128 |

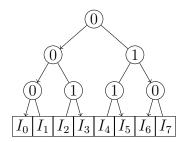

|   |     | 5.5.1  | Computing the Partitions                           | . 128 |

|   |     | 5.5.2  | Reachability of the Error State                    | . 131 |

|   |     | 5.5.3  | Checking if Two Machines are Right-Equivalent      | . 131 |

|   |     | 5.5.4  | Handling Counterexamples                           | . 132 |

|   | 5.6 | Evalua | ation                                              | . 132 |

|   | 5.7 | Relate | ed Work                                            | . 134 |

|   | 5.8 | Concl  | usions and Future Work                             | . 135 |

|   | 5.A |        | ndix: Proofs for Chapter 5                         |       |

| 6 | Mel | Min: S | SAT-Based Exact Minimization of Incompletely       |       |

|   |     |        | Mealy Machines                                     | 139   |

|   | 6.1 | Introd | luction                                            | . 139 |

|   |     | 6.1.1  |                                                    |       |

|   | 6.2 | Defini | tions                                              |       |

|   |     | 6.2.1  | Basic Definitions                                  |       |

|   |     | 6.2.2  | Problem Statement                                  |       |

|   |     | 6.2.3  | General Approach                                   |       |

|   | 6.3 |        | ed Work                                            |       |

|   | 6.4 |        | pach                                               |       |

|   | 0.1 | 6.4.1  | Incompatibility Matrix                             |       |

|   |     | 6.4.2  | Encoding as a SAT Problem                          |       |

|   |     | 6.4.3  | Computing a Partial Solution                       |       |

|   | 6.5 |        | mentation                                          |       |

|   | 0.0 | 6.5.1  | Dealing with Partially Specified Outputs           |       |

|   |     | J.J.1  | _ camo "in I artiary Specifica Outparts            |       |

# **CONTENTS**

|   |                   | 6.5.2                   | Dealing with Partially Specified Inputs          | 150                     |

|---|-------------------|-------------------------|--------------------------------------------------|-------------------------|

|   |                   | 6.5.3                   | Undefined Reset States                           | . 150                   |

|   | 6.6               | Evalua                  | ation                                            | . 150                   |

|   |                   | 6.6.1                   | Benchmarks                                       | . 151                   |

|   |                   | 6.6.2                   | Evaluation of MeMin                              | 155                     |

|   |                   | 6.6.3                   | Other Tools                                      | 155                     |

|   |                   | 6.6.4                   | Experimental Setup                               | . 158                   |

|   | 6.7               | Conclu                  | sions and Future Work                            | . 158                   |

|   | 6.A               | Appen                   | dix: Complete Benchmark Results                  | 159                     |

|   |                   |                         |                                                  |                         |

| 7 | Sun               | mary,                   | Conclusions, and Future Work                     | 165                     |

|   | <b>Sun</b><br>7.1 |                         | Conclusions, and Future Work ary and Conclusions |                         |

|   |                   |                         | •                                                | 165                     |

|   |                   | Summ. 7.1.1             | ary and Conclusions                              | . 165<br>. 165          |

|   |                   | Summo<br>7.1.1<br>7.1.2 | ary and Conclusions                              | . 165<br>. 165<br>. 166 |

|   | 7.1<br>7.2        | Summo<br>7.1.1<br>7.1.2 | ary and Conclusions                              | . 165<br>. 165<br>. 166 |

# Introduction

Modern microprocessors are among the most complex man-made systems. As a consequence, it is becoming increasingly difficult to predict, explain, or optimize the performance of software running on such microprocessors. As a basis, one needs detailed models of their microarchitectures.

Such models are, for example, required to build optimizing compilers, worst-case execution time (WCET) analyzers, cycle-accurate simulators, or self-optimizing software systems. Similarly, such models are necessary to show the presence or absence of microarchitectural security issues, such as Spectre and Meltdown [KHF<sup>+</sup>19, LSG<sup>+</sup>18]. Finally, detailed knowledge of microarchitectural details is also helpful when manually fine-tuning a piece of code for a specific processor.

Unfortunately, the documentation provided by hardware manufacturers is usually not detailed enough. To build microarchitectural models, engineers are thus often forced to perform measurements using microbenchmarks. Existing approaches typically require a significant amount of manual effort, and the results are not always accurate and precise.

The goal of this thesis therefore is to develop techniques for generating detailed models of microarchitectures automatically.

In the first part of the thesis, we focus on recent x86 microarchitectures. In particular, we develop techniques to automatically generate models for two properties that have a strong influence on the performance of software on a specific microarchitecture: the cache architecture and the latencies, throughputs, and port usages of individual instructions.

In the second part of the thesis, we look at more general techniques for obtaining models of hardware components. Specifically, we introduce the problem of *gray-box learning*, in which learning algorithms may exploit known information about the system to be learned.

# 1.1 Contributions and Structure of This Thesis

We now describe the addressed problems, and our approaches and contributions in more detail.

## nanoBench

In Chapter 2, we develop *nanoBench*, a tool for evaluating small microbenchmarks using hardware performance counters on x86 systems. Hardware performance counters are special-purpose registers that store the counts of various hardware-related events.

In contrast to previous tools, nanoBench can execute microbenchmarks directly in kernel space. This makes it possible to benchmark privileged instructions, and it allows for more accurate measurements by disabling interrupts and preemptions. Furthermore, this makes it also possible to directly access certain performance counters that are only available in kernel space; previous tools require expensive system calls to access such counters.

nanoBench provides the option to temporarily pause performance counting during specific parts of a microbenchmark. Furthermore, the reading of the performance counters is implemented with minimal overhead, avoiding function calls and branches. As a consequence, nanoBench is precise enough to measure, e.g., whether individual memory accesses result in cache hits or misses.

We use *nanoBench* to evaluate the microbenchmarks generated by the tools described in the following paragraphs.

## Instruction Characterizations

An aspect that has a relatively strong influence on performance is how ISA instructions decompose into micro-operations (µops), which ports these µops may be executed on, and what their latencies and throughputs are.

However, these properties are typically only poorly documented. Intel's processor manuals [Int12, Int19b], for example, only contain latency and throughput data for a number of "commonly-used instructions." They do not contain information on the decomposition of individual instructions into  $\mu$ ops, nor do they state the execution ports that these  $\mu$ ops can use.

The only way to obtain accurate instruction characterizations for many recent microarchitectures is thus to perform measurements using microbenchmarks.

#### 1.1. CONTRIBUTIONS AND STRUCTURE OF THIS THESIS

However, existing approaches, such as [Fog19], require significant manual effort to create suitable microbenchmarks and to interpret their results. Furthermore, the results are not always accurate and precise.

In Chapter 3, we develop a new approach that can automatically generate microbenchmarks in order to characterize the latency, throughput, and port usage of instructions on x86 CPUs in an accurate and precise manner.

Before describing our algorithms and their implementation, we first discuss common notions of instruction latency, throughput, and port usage. For the latency, we propose a new definition that, in contrast to previous definitions, considers dependencies between different pairs of input and output operands, which enables more accurate performance predictions.

We then develop algorithms that generate assembler code for microbench-marks to measure the properties of interest for most x86 instructions. Our algorithms take into account explicit and implicit dependencies, such as, e.g., dependencies on status flags. Therefore, they require detailed information on the x86 instruction set. To this end, we create a machine-readable XML representation of the x86 instruction set that contains all the information needed to automatically generate assembler code for every instruction. The relevant information is automatically extracted from the configuration files of Intel's x86 Encoder Decoder (XED) [Intc] library.

We have implemented our algorithms in a tool that we have successfully applied to 16 different Intel and AMD microarchitectures. The output of our tool is available both in the form of a human-readable, interactive HTML table and as a machine-readable XML file, so that it can be easily used to implement, e.g., simulators, performance prediction tools, or optimizing compilers.

Finally, we discuss several interesting insights obtained by comparing the results from our measurements with previously published data. Our precise latency data, for example, uncovered previously undocumented differences between different microarchitectures. It also explains discrepancies between previously published information. Apart from that, we uncovered various errors in Intel's IACA tool [Inta], and inaccuracies in the manuals.

# Characterizing Cache Architectures

To bridge the increasing latency gap between the processor and main memory, modern microarchitectures employ memory hierarchies with multiple levels of cache memory. These caches are small but fast memories that make use

#### **CHAPTER 1. INTRODUCTION**

of temporal and spatial locality. Typically, they have a big impact on the execution time of computer programs; the penalty of a miss in the last-level cache can be more than 200 cycles.

In Chapter 4, we develop techniques for creating models of cache architectures. We focus, in particular, on cache replacement policies, which are typically undocumented for recent microarchitectures.

To this end, we develop several tools for determining cache parameters. The first tool, *cacheInfo*, provides details on the *structure* of the caches, such as the sizes, the associativities, the number of cache sets, or the number of C-Boxes and slices.

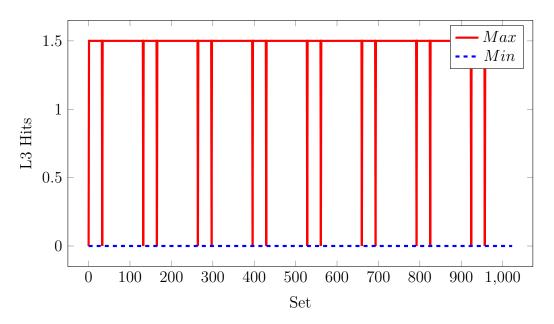

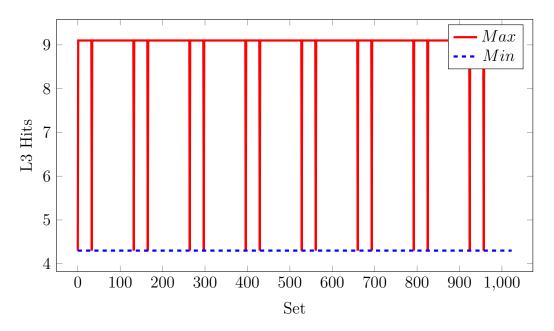

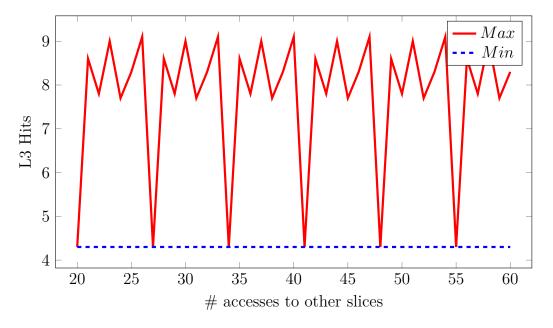

Our second tool, *cacheSeq*, makes it possible to analyze the *behavior* of the caches by measuring the number of cache hits and misses when executing an access sequence in one or more cache sets; the access sequence is supplied as a parameter to the tool and can be specified using a convenient syntax. To perform these measurements, the tool generates suitable microbenchmarks that are evaluated using *nanoBench*.

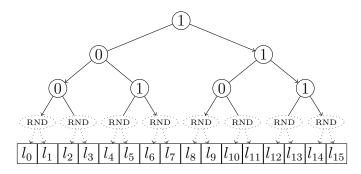

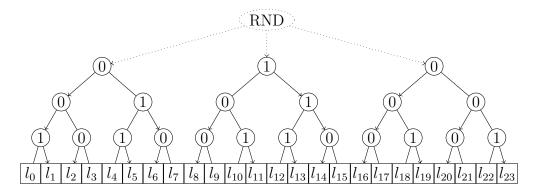

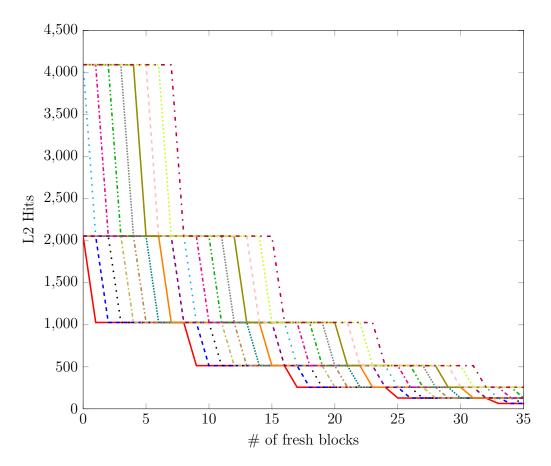

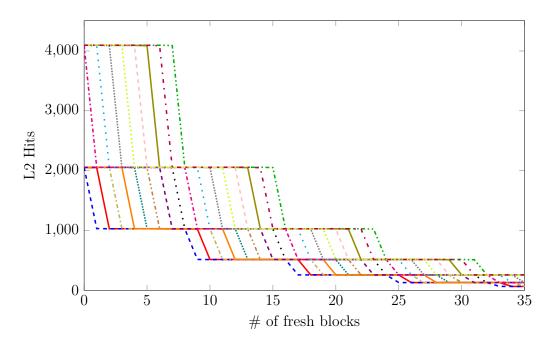

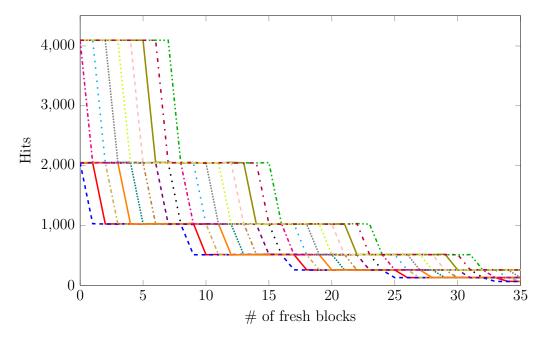

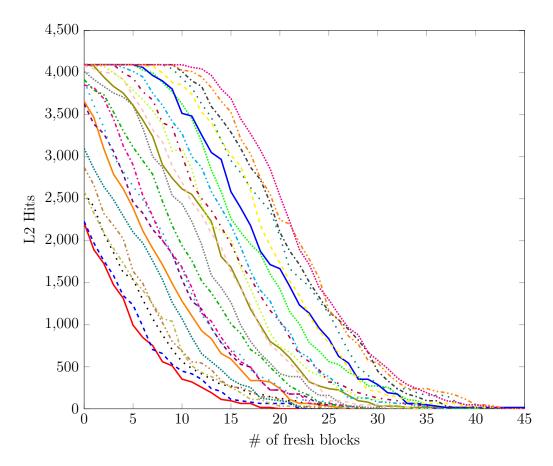

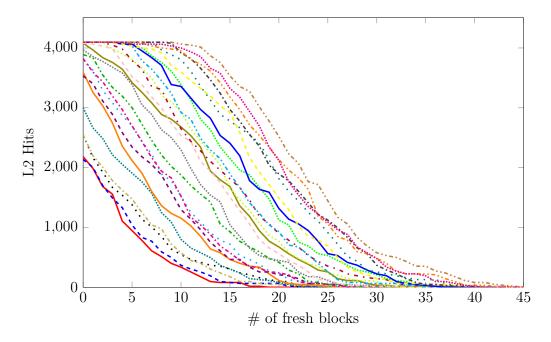

Based on *cacheSeq*, we then develop several tools for identifying the replacement policy. In particular, we implement a tool that can automatically infer permutation policies, and a tool that can automatically determine whether the policy belongs to a set of more than 300 variants of commonly used policies, including policies like MRU and QLRU, which are not permutation policies. These tools are precise enough to determine the policies used in individual cache sets. In addition to that, we develop a tool that can find out whether the cache uses an adaptive replacement policy. Furthermore, we propose a tool that creates *age graphs*, which are helpful for analyzing caches with nondeterministic replacement policies.

We have applied our tools to 13 different Intel microarchitectures, and we provide detailed models of their replacement policies. We have discovered several previously undocumented replacement policies.

# **Gray-Box Learning**

The algorithms we developed for Chapters 3 and 4 can be seen as instances of active learning approaches. Active learning (also called query learning) refers to a class of machine-learning techniques in which the learning algorithm is able to interact with the system to be learned.

However, the algorithms we developed for Chapters 3 and 4 are heavily targeted at the specific problems. In Chapter 5, we look at more general

#### 1.1. CONTRIBUTIONS AND STRUCTURE OF THIS THESIS

techniques. Specifically, we consider approaches for learning finite state machines, which are, in principle, suitable abstractions for modeling the behavior of microarchitectural components.

In active learning approaches, one commonly assumes an oracle, or teacher, that admits two kinds of queries about the system: output queries return the result of the system for a specific input, and equivalence queries check whether a conjectured model is consistent with the system to be learned and return a counterexample if not. Based on this setup, Angluin introduced the  $L^*$  algorithm [Ang87] for learning deterministic finite automata.  $L^*$  has since been extended to other modeling formalisms, such as Mealy machines [SG09], register automata [HSJC12, BHLM13, AFBKV15], or symbolic automata [MM14].

As the system is usually treated as a black box, no information about the internal structure of the system can be taken into account by most existing learning algorithms. In practice, however, systems are often composed of subcomponents, for some of which models might be available, but it is not possible to access the known and the unknown parts separately from the outside.

While it is in theory possible to learn a model of the entire system using existing black-box approaches, this is often not viable in practice because the state space is too large. A problem, which has received very little attention in the literature so far, is how to use the available information about the system to focus the learning algorithm on those parts that are unknown. We call this problem *gray-box learning*.

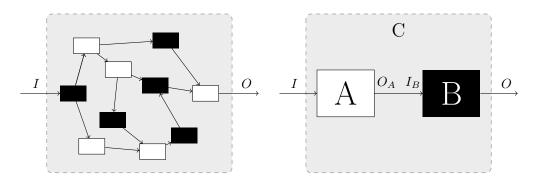

As a first step toward solving this problem, we study one specific instance. We consider the serial composition of two Mealy machines A and B, where A is known and B is unknown, and we assume that we can only perform queries on the composed machine.

While output queries can often be realized cheaply by measurements on the actual system, equivalence queries can usually only be approximated by a large number of such measurements. Our primary focus is thus to minimize the number of equivalence queries. We introduce an algorithm to exactly learn B in the context of A that performs at most |B| equivalence queries, where |B| denotes the number of states of B.

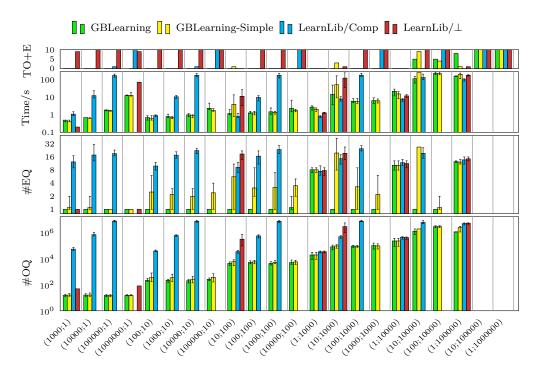

We evaluate our approach on compositions of randomly-generated machines against an implementation of the classic  $L^*$  algorithm in LearnLib [IHS15]. We show that our approach requires significantly fewer output and equivalence queries on most benchmarks.

## Minimization of Incompletely Specified Mealy Machines

It is generally a desirable property of models to be as small as possible. In Chapter 6, we take a fresh look at the problem of minimizing incompletely specified Mealy machines, i.e., machines where one or more outputs or next states might not be specified. While the minimization problem is efficiently solvable for fully specified machines [Hop71], it is NP-complete for incompletely specified ones [Pf173].

It turns out that this problem is quite closely related to the gray-box learning instance we studied in Chapter 5. A central algorithmic idea of our learning technique is a reduction to a Boolean satisfiability (SAT) problem. In Chapter 6, we show how a relatively straightforward adaptation of this reduction approach can be used to minimize incompletely specified Mealy machines.

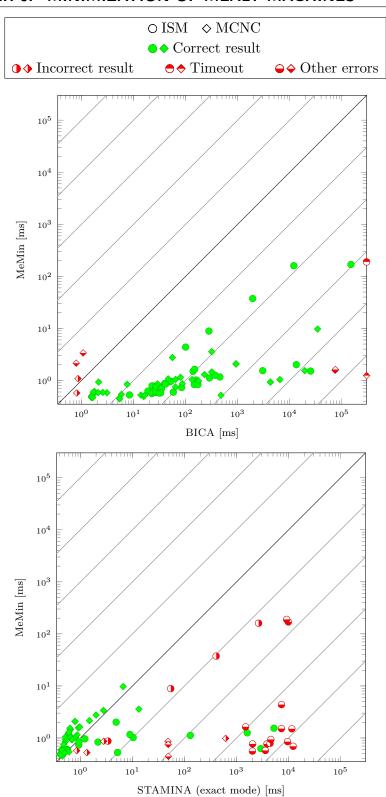

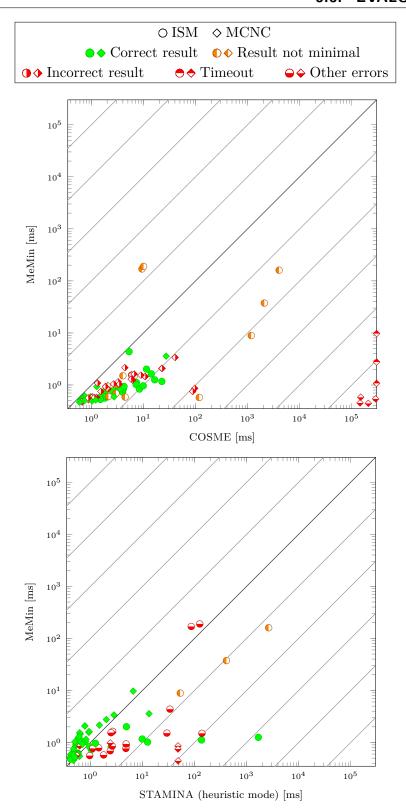

The minimization problem has been extensively studied before, and a number of exact and heuristic approaches have been proposed. We compare an implementation of our exact approach to several other approaches on two sets of standard benchmarks.

Our approach outperforms the other exact approaches significantly, in particular on a number of hard benchmarks. In some cases, it is faster than existing approaches by several orders of magnitude.

On most benchmarks, our approach is also competitive with state-of-the-art heuristic methods. There are only two benchmarks on which a heuristic approach is significantly faster. However, in these two cases, this heuristic approach is not able to find the minimal result.

## 1.2 Publications

Key parts of this thesis have been published in the following papers.

- [AR14]: Andreas Abel and Jan Reineke. Reverse engineering of cache replacement policies in Intel microprocessors and their evaluation. In *IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS), Monterey, CA, USA, March* 23–25, 2014, pages 141–142. © 2014 IEEE

- [AR15]: Andreas Abel and Jan Reineke. MeMin: SAT-based exact minimization of incompletely specified Mealy machines. In Proceedings of the IEEE/ACM International Conference on Computer-Aided Design (ICCAD), Austin, TX, USA, November 2–6, 2015, pages 94–101. © 2015 IEEE

- [AR16]: Andreas Abel and Jan Reineke. **Gray-box learning of serial compositions of Mealy machines.** In NASA Formal Methods—Proceedings of the 8th International Symposium, Minneapolis, MN, USA, June 7–9, 2016, pages 272–287. Springer-Verlag, 2016.

- [AR19]: Andreas Abel and Jan Reineke. uops.info: Characterizing latency, throughput, and port usage of instructions on Intel microarchitectures. In Proceedings of the Twenty-Fourth International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS), Providence, RI, USA, April 13–17, 2019, pages 673–686. ACM, 2019.

- [AR20]: Andreas Abel and Jan Reineke. nanoBench: A low-over-head tool for running microbenchmarks on x86 systems. In IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS), Boston, MA, USA, August 23–25, 2020. To appear. © 2020 IEEE

2

# nanoBench: A Low-Overhead Tool for Running Microbenchmarks on x86 Systems

In this chapter, we present nanoBench, a tool for evaluating small microbenchmarks using hardware performance counters on Intel and AMD x86 systems. Most existing tools and libraries are intended to either benchmark entire programs, or program segments in the context of their execution within a larger program. In contrast, nanoBench is specifically designed to evaluate small, isolated pieces of code. Such microbenchmarks are commonly used for analyzing undocumented hardware properties.

Unlike previous tools, nanoBench can execute microbenchmarks directly in kernel space. This allows to benchmark privileged instructions, and it enables more accurate measurements. The reading of the performance counters is implemented with minimal overhead, avoiding function calls and branches. As a consequence, nanoBench is precise enough to measure individual memory accesses.

Most of the work presented in this chapter has been published in [AR20].

## 2.1 Introduction

Benchmarking small pieces of code using hardware performance counters is often useful for analyzing the performance of software on a specific microprocessor, as well as for analyzing performance characteristics of the microprocessor itself.

#### **CHAPTER 2. NANOBENCH**

Such microbenchmarks can, e.g., be helpful in identifying bottlenecks in loop kernels. To this end, modern x86 CPUs provide many performance events that can be measured, such as cache hits and misses in different levels of the memory hierarchy, the pressure on execution ports, mispredicted branches, etc.

Low-level aspects of microarchitectures are typically only poorly documented. Thus, the only way to obtain detailed information is often through microbenchmarks using hardware performance counters. This includes, for example, the latency, throughput, and port usage of individual instructions (see Section 3.2.2). Microbenchmarks have also been used to infer properties of the memory hierarchy (see Section 4.5.1). In addition to that, such benchmarks have been used to identify microarchitectural properties that can lead to security issues, such as Spectre [KHF<sup>+</sup>19] and Meltdown [LSG<sup>+</sup>18].

Often, such microbenchmarks consist of two parts: The main part, and an initialization phase that, for example, sets registers or memory locations to specific values or tries to establish a specific microarchitectural state, e.g., by flushing the caches. Ideally, the performance counters should only be active during the main part.

To facilitate the use of hardware performance counters, a number of tools and libraries have been proposed. Most of the existing tools fall into one of two categories. First, there are tools that benchmark entire programs, such as perf [per], or profilers like Intel's VTune Amplifier [Intb]. Tools in the second category are intended to benchmark program segments that are executed in the context of a larger program. They usually provide functions to start and stop the performance counters that can be called before and after the code segment of interest. Such tools are, for example, PAPI [TJYD10] and libpfc [Bil].

Tools from both categories are not particularly well suited for microbench-marks of the kind described above. For tools from the first category, one obvious reason is that it is not possible to measure only parts of the code. Another reason is overhead. Just running a C program with an empty main function, compiled with a recent version of gcc, leads to the execution of more than 500,000 instructions and about 100,000 branches. Moreover, this number varies significantly from one run to another.

Overhead can also be a concern for tools from the second category. In PAPI, for example, the calls to start and stop the counters involve several hundred memory accesses, more than 150 branches, and for some counters even expensive system calls. This leads to unpredictable execution times and might, e.g., destroy the cache state that was established in the initialization part of the microbenchmark. Moreover, these calls will modify general-purpose

registers, so it is not possible to set the registers to specific values in the initialization part and use these values in the main part.

For several reasons, microbenchmarks often need to be run multiple times. One reason is the possibility of interference due to interrupts, preemptions or contention on shared resources that are also used by programs on other cores. Another reason are issues such as cold caches that impact the performance on the first runs. A third reason is that there are more performance events than there are programmable counters, so the measurements may need to be repeated with different counter configurations. Also, the code to be benchmarked itself often needs to be repeated several times. This is typically done by executing it in a loop or by unrolling it multiple times, or by a combination of both. All of this leads to a significant engineering effort that needs to be repeated over and over again.

In this chapter, we present  $nanoBench^1$ , an open-source tool that makes it very easy to evaluate small microbenchmarks on recent x86 CPUs. In Chapters 3 and 4, we describe techniques to automatically generate such microbenchmarks for characterizing the performance of instructions and for analyzing properties caches.

There are two variants of our tool: A user-space implementation and a kernel-space version. The kernel-space version makes it possible to directly benchmark privileged instructions, in contrast to any previous tool we are aware of. Furthermore, it allows for more accurate measurements than existing tools by disabling interrupts and preemptions. The tool is precise enough to measure, e.g., whether individual memory accesses result in cache hits or misses.

Microbenchmarks may use and modify any general-purpose and vector registers, including the stack pointer. After executing the microbenchmark, nanoBench automatically resets them to their previous values. The loop and unroll counts, as well as the number of repetitions and the aggregate function to be applied to the measurement results, can be specified via parameters.

# 2.2 Background

## 2.2.1 Hardware Performance Counters

Recent Intel and AMD processors are equipped with different types of hardware performance counters, i.e., special-purpose registers that store the counts of various hardware-related events. All of these counters can be read using

<sup>&</sup>lt;sup>1</sup>https://github.com/andreas-abel/nanoBench

the  $RDMSR^2$  instruction; many of them can also be read using the  $RDPMC^3$  instruction. The RDMSR instruction is a privileged instruction and can, thus, only be used in kernel space. The RDPMC instruction, on the other hand, is faster than the RDMSR instruction, and it can be directly accessed in user space if a specific flag in a control register is set.

#### **Core Performance Counters**

Each logical core has a private performance monitoring unit with multiple performance counters. There are two types of core performance counters:

#### • Fixed-Function Performance Counters

Recent Intel CPUs have three fixed-function performance counters that can be read with the *RDPMC* instruction. They count the number of retired instructions, the number of core cycles, and the number of reference cycles.

In addition to that, there are two fixed-function counters that are available both on recent Intel CPUs, as well as on AMD family 17h CPUs: the APERF counter, which counts core clock cycles, and the MPERF counter, which counts reference cycles. These two counters can only be accessed with the RDMSR instruction and are, thus, only available in kernel space.

#### • Programmable Performance Counters

Recent Intel CPUs have between two and eight, and AMD family 17h CPUs have six programmable performance counters. They can be programmed with a large number of different performance events (more than 200 on some CPUs), such as the number of  $\mu$  post that use a specific port, the number of cache misses in different levels of the memory hierarchy, the number of mispredicted branches, etc. These counters can be read with the RDPMC instruction.

## Uncore/L3 Performance Counters

In addition to the per-core performance counters described above, recent processors also have a number of programmable global performance counters that can, in particular, count events related to the shared L3 caches. On Intel CPUs, these counters can only be read in kernel space.

<sup>&</sup>lt;sup>2</sup>"Read from model specific register"

<sup>&</sup>lt;sup>3</sup>"Read performance-monitoring counters"

## 2.2.2 Assembler Instructions

Throughout this thesis, we use assembler instructions in Intel syntax. They have the following form:

The mnemonic identifies the operation, e.g., ADD or XOR. The first operand  $op_1$  is typically the destination operand, and the other operands are the source operands (an operand can also be both a source and destination operand). Operands can be registers, memory locations, or immediates. Memory operands use the syntax

$$[R_{base} + R_{index} * scale + disp],$$

where  $R_{base}$  and  $R_{index}$  are general-purpose registers, disp is an integer, and scale is 1, 2, 4, or 8. All of these components are optional and can be omitted.

In addition to these explicit operands, an instruction can also have implicit operands. As an example, consider the following instruction:

This instruction computes the sum of the general-purpose register RAX and the memory at the address of register RBX, and stores the result in RAX. We refer to RAX and [RBX] as *explicit* operands. In addition to that, the instruction updates the status flags (e.g., the carry flag) according to the result. The status flags are *implicit* operands of the ADD instruction.

There are often multiple variants of an instruction with different operand types and/or widths.

Note that there is not always a one-to-one correspondence between assembler code and machine code. Sometimes, there are multiple possible encodings for the same assembler instruction. It is, in general, not possible to control which of these encodings the assembler selects. Thus, some machine instructions cannot be generated using assembler code.

## 2.3 Features

In this section, we first give a high-level overview by looking at a simple example that shows how *nanoBench* can be used. We then describe various features of *nanoBench* in more detail.

## 2.3.1 Example

The following example shows how *nanoBench* can be used to measure the latency of the L1 data cache on a Skylake-based system.

```

./nanoBench.sh -asm "mov R14, [R14]"

-asm_init "mov [R14], R14"

-config cfg_Skylake.txt

```

The tool will first execute the instruction

```

mov [R14], R14,

```

which copies the value of register R14 to the memory location that R14 points to. *nanoBench* always initializes R14 (and a number of other registers) to point into a dedicated memory area that can be freely modified by microbenchmarks; this is described in more detail in Section 2.3.7.

nanoBench then starts the performance counters and executes the instruction

multiple times. The number of repetitions can be controlled via parameters; for more information see Section 2.3.6. The instruction loads the value at the address in R14 into R14. Thus, the execution time of this instruction corresponds to the L1 data cache latency. Afterwards, *nanoBench* stops the performance counters. The entire benchmark is then repeated multiple times to obtain stable results.

The output of *nanoBench* will be similar to the following:

```

Instructions retired: 1.00

Core cycles: 4.00

Reference cycles: 3.52

UOPS_ISSUED.ANY: 1.00

UOPS_DISPATCHED_PORT.PORT_0: 0.00

UOPS_DISPATCHED_PORT.PORT_1: 0.00

UOPS_DISPATCHED_PORT.PORT_2: 0.50

UOPS_DISPATCHED_PORT.PORT_3: 0.50

UOPS_DISPATCHED_PORT.PORT_4: 0.00

UOPS_DISPATCHED_PORT.PORT_5: 0.00

MEM_LOAD_RETIRED.L1_HIT: 1.00

MEM_LOAD_RETIRED.L2_HIT: 0.00

MEM_LOAD_RETIRED.L3_HIT: 0.00

MEM_LOAD_RETIRED.L3_MISS: 0.00

```

The first three lines show the result of the fixed-function performance counters. The remaining lines correspond to the performance events specified in the cfg\_Skylake.txt configuration file that was supplied as a parameter in the nanoBench call shown above; details on configuration files are described in Section 2.3.10.

From the results, we can conclude that the L1 data cache latency is 4 cycles. This agrees with the documentation in Intel's optimization manual [Int19b].

#### 2.3.2 Generated Code

To execute a microbenchmark, *nanoBench* first generates code for a function similar to the pseudocode shown in Algorithm 2.1.

In line 2, the generated code first saves the current values of the registers to the memory and initializes certain registers to point to specific memory locations (see Section 2.3.7). Then, the initialization part of the microbenchmark is executed (line 3). In the next line (line 4), the performance counters are read. Unless the noMem option (see Section 2.3.9) is used, this step does not modify the values in any general-purpose or vector registers that were set by the initialization code (technically, it does modify certain registers temporarily, but it resets them to their previous value before the next line is executed).

Lines 5 to 9 contain the code for the main part of the microbenchmark. The code is unrolled multiple times (this can be configured via a parameter, see Section 2.3.6). If the parameter *loopCount* is larger than 0, the code for a for-loop is inserted in line 5; in this case, the code of the microbenchmark must not modify register R15, which is used to store the loop counter.

Afterwards, the performance counters are read a second time (line 10), and in line 11, the registers are restored to the values that were saved in line 2. Finally, the difference between the two performance counter values, divided by the number of repetitions, is returned.

# 2.3.3 Running the Generated Code

Algorithm 2.2 shows how the generated code is run. The code is run a configurable number of times. At the end, an aggregate function is applied to the measurement results, which can be either the minimum, the median, or the arithmetic mean (excluding the top and bottom 20% of the values). A configurable number of runs in the beginning can be excluded from the result; this is described in more detail in Section 2.3.8.

#### **CHAPTER 2. NANOBENCH**

By default, nanoBench generates and runs two versions of the code: the first one with localUnrollCount set to the specified unrollCount, and the second time with localUnrollCount set to two times the specified unrollCount. The reported result is the difference between the two runs. This removes the overhead of the measurement instructions from the result, as well as anomalies that might be caused by the serialization instructions that are needed before and after reading the performance counters (see also Section 2.4.1).

nanoBench also provides an option that uses a localUnrollCount of 0 for one of the runs instead (i.e., there are no instructions between line 4 and line 10 in this case).

## Algorithm 2.1: Generated code for a microbenchmark

```

1 Function generatedCode()

saveRegs

\mathbf{2}

codeInit

3

m1 \leftarrow \text{readPerfCtrs}

// stores results in memory,

4

// does not modify registers

for j \leftarrow 0 to loopCount do

// this line is omitted

\mathbf{5}

// if loopCount=0

code // copy #1

code // copy #2

7

8

code // copy #localUnrollCount

9

m2 \leftarrow \text{readPerfCtrs}

10

restoreRegs

11

r \leftarrow (m2 - m1)/(max(1, loopCount) * localUnrollCount)

12

return r

13

```

## Algorithm 2.2: Running a microbenchmark

```

Function run(code)2for i \leftarrow -warmUpCount to nMeasurements do3m \leftarrow code()4if i \geq 0 then// ignore warm-up runs5measurements[i] \leftarrow m6return agg(measurements)// apply aggregate function

```

# 2.3.4 Kernel/User Mode

nanoBench is available in two versions: A user-space and a kernel-space version. The kernel-space version has several advantages over the user-space version:

- It makes it possible to benchmark privileged instructions.

- It can allow for more accurate measurement results as it disables interrupts and preemptions during measurements.

- It can use several performance counters that are not accessible from user space, like the uncore counters on Intel CPUs, or the APERF and MPERF counters.

- It can allocate physically-contiguous memory. See also Section 2.3.7.

On the other hand, executing microbenchmarks in kernel space can lead to potential data loss and security problems if the microbenchmarks contain bugs. It is thus recommended to use the kernel-space version only on dedicated test machines.

#### 2.3.5 Interface

We provide a unified interface to the user-space and the kernel-space version in the form of two shell scripts, nanoBench.sh and kernel-nanoBench.sh, that have mostly the same command-line options.

In addition to that, we also provide a Python interface for the kernel-space version. This interface is used for the tools described in Chapters 3 and 4.

With all interfaces, the code of the microbenchmarks can be specified either as an assembler code sequence in Intel syntax (like in the example in Section 2.3.1), or by the name of a binary file containing x86 machine code.

# 2.3.6 Loops vs. Unrolling

For microbenchmarks that have code that needs to be repeated several times to obtain meaningful results, there is a trade-off between unrolling the code (i.e., creating multiple copies of it) and executing the code in a loop.

Using a loop has the advantage of keeping the code size small, so that it will fit into the cache. On the other hand, the loop introduces an additional overhead, which can be significant if the body of the loop is small.

#### **CHAPTER 2. NANOBENCH**

Whether unrolling or a loop should be used, depends on the particular benchmark. For benchmarks that measure, e.g., the number of data cache misses, a loop is the better choice, as it does not introduce any overhead in terms of memory accesses. On the other, for a benchmark that measures the port usage of an instruction, using only unrolling is better, as otherwise, the  $\mu$ ops of the loop code compete for ports with the  $\mu$ ops of the benchmark. For some benchmarks, a combination of both a loop and unrolling yields the best results.

nanoBench provides two parameters, loopCount and unrollCount, that control the number of loop iterations, and how often the code is unrolled.

## 2.3.7 Accessing Memory

nanoBench initializes the registers RSP (i.e., the stack pointer), RBP (i.e., the base pointer), RDI, RSI, and R14 to point into dedicated memory areas (of 1 MB each) that can be freely modified by the microbenchmarks.

Furthermore, for microbenchmarks needing a larger memory area, like benchmarks for determining cache parameters, the kernel version of *nanoBench* provides an option for reserving a physically-contiguous memory area of a configurable size (see also Section 2.4.4).

## 2.3.8 Warm-Up Runs

nanoBench provides the option of performing a configurable number of initial benchmark runs that are excluded from the results. This can, for example, be useful to make sure that the code and other accessed memory locations are in the cache. It can also be used to train the branch predictor to reduce the number of mispredicted branches. Furthermore, there are some instructions that require a warm-up period after having not been used for a while before they can execute at full speed again, like AVX2 instructions on some microarchitectures.

#### 2.3.9 noMem Mode

By default, the code to read the performance counters writes the results to the memory. After a warm-up run, this memory location is usually in the cache, and thus, the time for these memory operations is constant.

However, for microbenchmarks that contain many memory accesses to different addresses that map to the same cache set, writing the performance counter results to the memory can be problematic. One reason for this is that the memory accesses in line 4 may change a cache state that was established by the initialization part of the benchmark. Another reason is that the microbenchmark code may evict the block that stores the performance counter results, which would lead to additional cache misses.

To avoid these problems, nanoBench has a special mode that stores all performance counter measurements in registers instead of in memory. If this mode is used, certain general-purpose registers must not be modified by the microbenchmark.

Moreover, if this mode is used, *nanoBench* also provides a feature to temporarily pause performance counting. This feature can be used by including special magic byte sequences in the microbenchmark code for stopping and resuming performance counting. Using this feature incurs a certain timing overhead, so it is in particular useful for benchmarks that do not measure the time but, e.g., the number of cache hits or misses.

## 2.3.10 Performance Counter Configurations

The performance events to be measured are specified in a configuration file. The file uses a simple syntax to define the events. Unlike in some previous tools, like libpfc [Bil], the events are not hard-coded, which makes it easy to adapt *nanoBench* to future CPUs, as only a new configuration file has to be created.

If the configuration file contains more events than there are programmable performance counters, the benchmarks are automatically executed multiple times with different counter configurations.

We provide configuration files with all events for all recent Intel microarchitectures and the AMD Zen microarchitecture.

## 2.3.11 Execution Time of nanoBench

Evaluating microbenchmarks with nanoBench is very fast. As an example, we consider a benchmark consisting of a single NOP instruction, that is run with unrollCount = 100, loopCount = 0, nMeasurements = 10, and a configuration file with four events. On an Intel Core i7-8700K, running nanoBench with these parameters takes about 15 ms for the kernel version (assuming that the kernel module is already loaded), and about 50 ms for the user-space version.

## 2.3.12 Supported Platforms

We have successfully used *nanoBench* on processors from most generations of Intel's Core microarchitecture and with AMD Ryzen CPUs. All experiments were performed under Ubuntu 18.04, but *nanoBench* should be compatible with any Linux distribution that uses a recent kernel version.

# 2.4 Implementation

#### 2.4.1 Accurate Performance Counter Measurements

## Serializing Instruction Execution

As described in Section 2.2, performance counters can be read with the *RDPMC* or the *RDMSR* instruction. These instructions are not serializing instructions. Thus, due to out-of-order execution (see Section 3.3), they may be reordered with earlier or later instructions by the processor. For obtaining meaningful measurement results, it is therefore important to add instructions that serialize the instruction stream both before and after any instructions that read performance counters.

Previous approaches (e.g., [Fog]) often use the *CPUID* instruction for that purpose. However, for benchmarking short code segments, this is problematic. One reason for this is that the *CPUID* instruction has a variable latency and µop count. Paoloni [Pao10] observed that the execution time of the *CPUID* can differ by hundreds of cycles from run to run. The variable µop count can be eliminated by setting the register RAX to a fixed value before each execution of the *CPUID* instruction; this also reduces the variance in the execution time, but does not fully eliminate it. Moreover, for an instruction sequence of the form

#### A; CPUID; B,

the serialization property of the CPUID instruction only guarantees that all  $\mu$ ops of A have completed before B is fetched and executed. It does not guarantee that all  $\mu$ ops of A have completed before the first  $\mu$ op of the CPUID instruction is executed, and it does also not guarantee that all  $\mu$ ops of the CPUID instruction have completed before the first  $\mu$ op of B is executed.

We propose to use the LFENCE instruction instead. This instruction is not fully serializing: it does not guarantee that earlier stores have become globally visible, and subsequent instructions may be fetched from memory before LFENCE completes. However, on Intel CPUs it does guarantee that

"LFENCE does not execute until all prior instructions have completed locally, and no later instruction begins execution until LFENCE completes" [Int19c]. For our purposes, this is sufficient, and the guarantee is even somewhat stronger than that for the CPUID instruction, as it also orders the LFENCE instruction itself with respect to the preceding and succeeding instructions. On AMD CPUs, the LFENCE provides similar guarantees if Spectre mitigations are enabled. Using the LFENCE instruction for measurements of short durations was also recently recommended by McCalpin [McC18].

#### Reducing Interference

In the kernel-space version, we disable preemptions and hard interrupts during measurements, as they can perturb the measurement results [WM08, WTM13]. This is not possible for the user-space version; however, we do pin the process to a specific core in this case to avoid the cost of process switches between cores.

Furthermore, for obtaining unperturbed measurement results, we recommend disabling hyper-threading. When using performance counters for resources shared by multiple cores, such as L3 caches, we furthermore recommend disabling all cores that share these resources. We provide shell scripts for this in our repository.

For microbenchmarks that measure properties of caches, such as the benchmarks described in Chapter 4, it can be helpful to disable cache prefetching. On Intel CPUs, this can be achieved by setting specific bits in a model-specific register (MSR). Details on how to do this are available in the documentation of nanoBench.

# 2.4.2 Generating Code

As described in Section 2.3, nanoBench runs microbenchmarks by generating a function that contains the code of the microbenchmark, as well as setup and measurement instructions. This is implemented by first allocating a large enough memory area and marking it as executable. Then, the corresponding machine code is written to this memory area, including unrollCount many copies of the code of the microbenchmark. If this code contains the magic byte sequences for pausing performance counting as described in Section 2.3.9, they are replaced by corresponding machine code for reading performance counters.

Generating the code for executing the microbenchmarks at runtime in this way makes it possible to access the performance counters without having to execute any function calls or branches.

## 2.4.3 Kernel Module

The kernel-space version of *nanoBench* is implemented as a kernel module. While the module is loaded, it provides a set of virtual files that are used to configure and run microbenchmarks. For example, setting the loop count, or the code of the microbenchmark is done by writing the corresponding values to specific files under /sys/nb/. Reading the file /proc/nanoBench generates the code for running the benchmark (as described in Section 2.4.2), runs the benchmark (possibly multiple times, depending on the configuration), and returns the result of the benchmark.

Note that it is usually not necessary to access these virtual files directly, as we provide convenient interfaces that perform these accesses automatically (see Section 2.3.5).

## 2.4.4 Allocating Physically-Contiguous Memory

In Linux kernel code, the kmalloc function can be used to allocate physically-contiguous memory. However, with recent kernel versions, this is limited to at most  $4\,\mathrm{MB}$ .

Some of the microbenchmarks for determining properties of the L3 caches that we describe in Chapter 4 require larger memory areas. We are not aware of a way to directly allocate larger physically-contiguous memory areas. However, we noticed that in many cases, subsequent calls to *kmalloc* yield adjacent memory areas. This is, in particular, the case if the system was rebooted recently. Moreover, the corresponding virtual addresses are also adjacent.

Based on this observation, we implemented a greedy algorithm that tries to find a physically-contiguous memory area of the requested size by performing multiple calls to kmalloc. If this does not succeed, the tool proposes a reboot. Note that allocating memory is only necessary once when the kernel module is loaded, and not before each microbenchmark run.

## 2.5 Related Work

Perf [per] and Intel's VTune Amplifier [Intb] are two examples of tools that are targeted at analyzing whole programs using hardware performance counters. Tools from this category can often display performance statistics at different levels of granularity, sometimes for individual source code lines. However, this data is usually obtained via sampling and, thus, not precise. Such tools are commonly used for identifying the parts of a program that would most benefit from further optimizations.

PAPI [TJYD10] is a widely used tool for accessing performance counters. It provides C and Fortran interfaces that provide functions for configuring and reading performance counters. It can be used for measuring the performance of smaller code segments in the context of a larger program. However, reading the performance counters leads to multiple function calls, branches, and memory accesses. Therefore, it is not suitable for the class of microbenchmarks considered in this thesis.

LIKWID [THW10] is a tool suite providing multiple performance analysis tools. It can both benchmark whole programs, as well as, similar to *PAPI*, specific code regions of a larger program. Reading the performance counters requires expensive system calls [RTHW14].

libpfc [Bil] is a library that was designed in a way to make it possible to use performance counters with a very low overhead. It provides macros with inline assembler code for reading the performance counters. Thus, it does not require function calls or branches. Like our tool, it uses the LFENCE instruction to serialize the instruction stream. In fact, a very early version of our tool was based on libpfc. However, libpfc only supports Haswell CPUs, and it does not support accessing uncore performance counters.

Agner Fog [Fog] provides a framework for running microbenchmarks similar to the microbenchmarks considered in this thesis. The code of the microbenchmark, which is not allowed to use all registers, must be inserted into specific places in a file provided by the framework. The overhead for reading performance counters is relatively small; it does not require function calls or branches. However, the tool uses the *CPUID* instruction for serialization, which can be problematic for short microbenchmarks, as described in Section 2.4.1. The tool only supports a relatively small number of performance events, and it only supports performance counters that can be read with the *RDPMC* instruction (i.e., it does not support uncore counters on Intel CPUs, or the APERF/MPERF counters).

In concurrent work, Chen et al. [CBM+19] present a tool for benchmarking basic blocks using the core cycles, and the L1 data and instruction cache performance counters. Unlike similar tools, Chen et al.'s tool supports microbenchmarks that can make arbitrary memory accesses; this is implemented by automatically mapping all accessed virtual memory pages to a single physical page. The tool was used to train Ithemal [MRAC19], which is a basic block throughput predictor that is based on a neural network. Chen et al. also propose a benchmark suite, called BHive, that consists of more than 300,000 basic blocks, and they use their tool to obtain throughput measurements for these basic blocks on CPUs with the Ivy Bridge, Haswell, and Skylake microarchitectures. The code that reads the performance counters contains branches, and it uses the *CPUID* instruction for serialization; however, it lacks a serialization instruction after reading the core cycles counter for the first time. As a consequence, the measurement results are relatively noisy. For Skylake, for example, we found in the BHive benchmark suite about 20,000 basic blocks that have instructions with memory operands, but a measured throughput value smaller than 0.5; for more than 2,200 of these blocks, the measured throughput value was even smaller than 0.45<sup>4</sup>. These throughput values are obviously incorrect, since Skylake can execute at most two instructions with memory operands per cycle. Chen et al. compare their measurement results with predictions from Ithemal and several other throughput prediction tools, including Intel's IACA (see also Section 3.2.1). As the average deviation of Ithemal's predictions from the measured throughputs is smaller than the average deviations of the other tools, the authors conclude that Ithemal outperforms the other tools.

None of the existing tools that we are aware of allows for executing benchmarks directly in kernel space.

# 2.6 Conclusions and Future Work

We have presented a new tool that significantly reduces the engineering effort required for evaluating small microbenchmarks in an accurate and precise way.

We demonstrate the usefulness of our tool in the following two chapters. In Chapter 3, we show how it can be used to characterize the latency, throughput, and port usage of x86 instructions. In Chapter 4, we use *nanoBench* to evaluate microbenchmarks for analyzing cache properties.

<sup>&</sup>lt;sup>4</sup>https://github.com/ithemal/bhive/issues/1

#### **Future Work**

On Intel CPUs, the performance counters can be configured in way such that when one of the counters overflows, all counters stop counting. Recently, Brandon Falk [Fal19] proposed an approach that uses this feature in a creative way to get cycle-by-cycle performance data. The main idea is to set the value of the core cycles counter to N cycles below overflow before the measurements, and to repeat the measurements multiple times with different values for N. Falk implemented this technique in a custom CPU research kernel, called  $Sushi\ Roll$ , that is, unfortunately, not publicly available. We plan to add a similar functionality to nanoBench.

Furthermore, we would also like to adapt *nanoBench* to non-x86 architectures, such as ARM, MIPS, or RISC-V [WLPA14].

# 3

# uops.info:

# Characterizing the Latency, Throughput, and Port Usage of Instructions on x86 Microarchitectures

In this chapter, we present the design and implementation of a tool to construct faithful models of the latency, throughput, and port usage of x86 instructions.

To this end, we first discuss common notions of instruction throughput and port usage, and introduce a more precise definition of latency that, in contrast to previous definitions, considers dependencies between different pairs of input and output operands.

We then develop novel algorithms to infer the latency, throughput, and port usage based on automatically-generated microbenchmarks that are more accurate and precise than existing work. The microbenchmarks are evaluated using *nanoBench* (see Chapter 2).

The output of our tool is provided both in the form of a human-readable, interactive HTML table and as a machine-readable XML file.

We provide experimental results for many recent microarchitectures and discuss various cases where the output of our tool differs considerably from prior work.

This chapter is an extended version of [AR19]. We analyze seven additional microarchitectures (including two from AMD) and more than 10,000 additional instruction variants. Furthermore, we provide a more detailed description of our algorithms and an enhanced evaluation.

## 3.1 Introduction

Developing tools that predict, explain, or even optimize the performance of software is challenging due to the complexity of today's microarchitectures. Unfortunately, this challenge is exacerbated by the lack of a precise documentation of their behavior.

While the high-level structure of modern microarchitectures is well-known and stable across multiple generations, lower-level aspects may differ considerably between microarchitecture generations and are generally not as well documented. An important aspect with a relatively strong influence on performance is how ISA instructions decompose into micro-operations (µops), which ports these µops may be executed on, and what their latencies are.

Knowledge of this aspect is required, for instance, to build performance-analysis tools like CQA [CRON+14], Kerncraft [HHEW15], UFS [PWKJ16], llvm-mca [Bia18], or OSACA [LHH+18, LHHW19]. It is also useful when configuring cycle-accurate simulators like Zesto [LSX09], gem5 [BBB+11], McSim+ [ALOJ13], or ZSim [SK13]. Optimizing compilers, such as GCC [GCC] or LLVM [LA04], can profit from detailed instruction characterizations to generate efficient code for a specific microarchitecture. Similarly, such knowledge can be helpful when manually fine-tuning a piece of code for a specific processor.

Unfortunately, information about the port usage, latency, and throughput of individual instructions at the required level of detail is hard to come by. Intel's processor manuals [Int12, Int19b] only contain latency and throughput data for a number of "commonly-used instructions." They do not contain information on the decomposition of individual instructions into µops, nor do they state the execution ports that these µops can use.

The only way to obtain accurate instruction characterizations for many recent microarchitectures is thus to perform measurements using microbenchmarks. Such measurements are aided by the availability of performance counters that provide precise information on the number of elapsed cycles and the cumulative port usage of instruction sequences. A relatively large body of work (see Section 4.5.1) uses microbenchmarks to infer properties of the memory hierarchy. Another line of work [JEJI08, GJB<sup>+</sup>10, GJ11, BBG<sup>+</sup>12] uses automatically generated microbenchmarks to characterize the energy consumption of microprocessors. Comparably little work [CRON<sup>+</sup>14, Fog19, Gra17, Ins] is targeted at instruction characterizations. Furthermore, existing approaches, such as [Fog19], require significant manual effort to create the

microbenchmarks and to interpret the results of the experiments. Furthermore, its results are not always accurate and precise, as we will show later.

In this chapter, we develop a new approach that can automatically generate microbenchmarks in order to characterize the latency, throughput, and port usage of instructions on x86 CPUs in an accurate and precise manner.

Before describing our algorithms and their implementation, we first discuss common notions of instruction latency, throughput, and port usage. For the latency, we propose a new definition that, in contrast to previous definitions, considers dependencies between different pairs of input and output operands, which enables more accurate performance predictions.

We then develop algorithms that generate assembler code for microbench-marks to measure the properties of interest for most x86 instructions. Our algorithms take into account explicit and implicit dependencies, such as, e.g., dependencies on status flags. Therefore, they require detailed information on the x86 instruction set. We create a machine-readable XML representation of the x86 instruction set that contains all the information needed to automatically generate assembler code for every instruction. The relevant information is automatically extracted from the configuration files of Intel's x86 Encoder Decoder (XED) [Intc] library.

We have implemented our algorithms in a tool that we have successfully applied to 16 different Intel and AMD microarchitectures. In addition to running the generated microbenchmarks on the actual hardware using nanoBench (see Chapter 2), we have also implemented a variant of our tool that runs them on top of IACA [Inta]. IACA is a closed-source tool published by Intel that can statically analyze the performance of loop kernels on different Intel microarchitectures. It is, however, not updated anymore and its results are not always accurate, as we will show later.

The output of our tool is available both in the form of a human-readable, interactive HTML table and as a machine-readable XML file, so that it can be easily used to implement, e.g., simulators, performance prediction tools, or optimizing compilers.

Finally, we discuss several interesting insights obtained by comparing the results from our measurements with previously published data. Our precise latency data, for example, uncovered previously undocumented differences between different microarchitectures. It also explains discrepancies between previously published information. Apart from that, we uncovered various errors in IACA, and inaccuracies in the manuals.

#### 3.2 Related Work

In this section, we describe existing sources of detailed instruction data for recent Intel and AMD microarchitectures. We first consider information provided by the manufacturers directly and then look at measurement-based approaches.

## 3.2.1 Information Provided by the Manufacturers

#### Intel

Intel's Optimization Reference Manuals [Int12, Int19b] contain a set of tables with latency and throughput data for "commonly-used instructions." The tables are not complete; for some instructions, only throughput information is provided. The manuals do not contain detailed information about the port usage of individual instructions.

For the most recent microarchitecture (Ice Lake), Intel provides a machinereadable file with latency and throughput numbers for a relatively large number of instruction variants [Int19a]. However, the file does not contain information on the port usage of these instruction variants.

IACA [Inta] is a closed-source tool developed by Intel that can statically analyze the performance of loop kernels on several microarchitectures (which can be different from the system that the tool is run on). The tool generates a report which includes throughput and port usage data of the analyzed loop kernel. By considering loop kernels with only one instruction, it is possible to obtain the throughput of the corresponding instruction. However, it is, in general, not possible to determine the port bindings of the individual µops this way. Early versions of IACA were also able to analyze the latency of loop kernels; however, support for this was dropped in version 2.2. As of April 2019, IACA has reached its "End Of Life".

The instruction scheduling components of LLVM [LA04] for Sandy Bridge, Haswell, Broadwell, and Skylake were recently updated and extended with latency and port usage information that was, according to the commit message<sup>2</sup>, provided by the architects of these microarchitectures. The resulting models are available in the LLVM repository.

<sup>&</sup>lt;sup>1</sup>https://software.intel.com/en-us/articles/intel-architecture-code-analyzer

<sup>&</sup>lt;sup>2</sup>https://reviews.llvm.org/rL307529

#### AMD

AMD provides a spreadsheet with latency, throughput, and port usage data for Family 17h processors [AMD17]. This data "is based on estimates and is subject to change." The document was last updated in 2017, when Zen was AMD's current microarchitecture. It is unclear in how far the data also applies to CPUs with the Zen+ or the Zen 2 microarchitecture, which are also Family 17h processors.

# 3.2.2 Measurement-Based Approaches

Agner Fog [Fog19] provides lists of instruction latency, throughput, and port usage data for different x86 microarchitectures. The data in the lists is not complete; for example, latency data for instructions with memory operands is often missing. The port usage information is sometimes inaccurate or imprecise; we discuss reasons for this in Section 3.5.1. The data is obtained using a set of test scripts developed by the author. These test scripts generate microbenchmarks that are evaluated using Fog's measurement framework (see Section 2.5). The outputs of the microbenchmarks have to be interpreted manually to build the instruction tables.

CQA [CRON+14] is a performance analysis tool for x86 code that requires latency, throughput, and port usage data to build a performance model of a microarchitecture. It includes a microbenchmark module that supports measuring the latency and throughput of many x86 instructions. For non-supported instructions, the authors use Agner Fog's instruction tables [Fog19]. The paper briefly mentions that the module can also measure the number of pops that are dispatched to execution ports using performance counters, but no further details are provided.

EXEgesis [Goo] is a project that can create a machine-readable list of instructions by parsing the PDF representation of Intel's *Software Developer's Manual* [Int19c]. One of the goals of the project is also to infer latencies and pop scheduling information for different instruction and microarchitecture pairs.

Granlund [Gra17] presents measured latency and throughput data for different x86 processors. He considers only a relatively small subset of the x86 instruction set.

AIDA64 [Fin] is a commercial, closed-source system information tool that can perform throughput and latency measurements of x86 instructions. Results for many processors obtained using AIDA64 are available at [Ins].

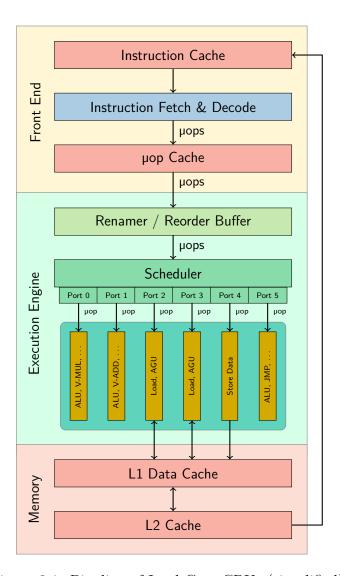

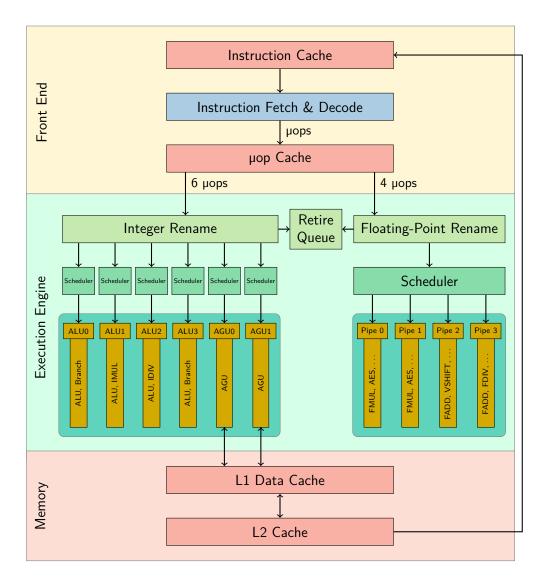

Figure 3.1: Pipeline of Intel Core CPUs (simplified)

# 3.3 Background

In this section, we describe the pipelines of recent Intel and AMD x86 processors.

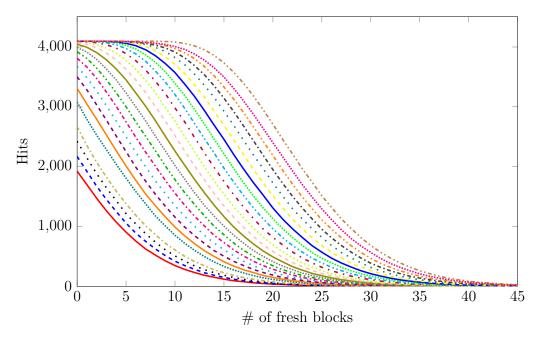

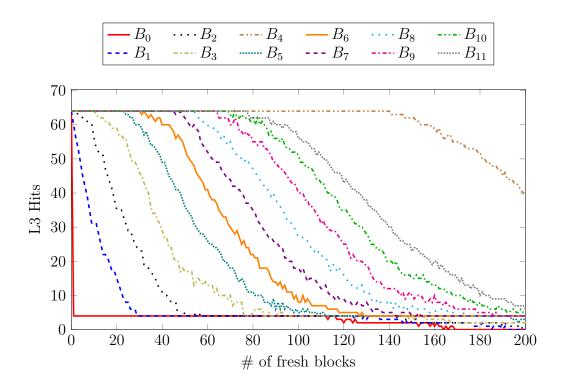

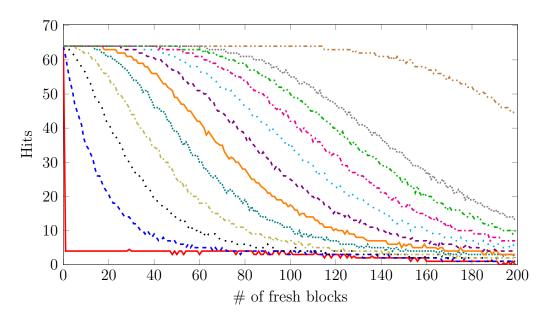

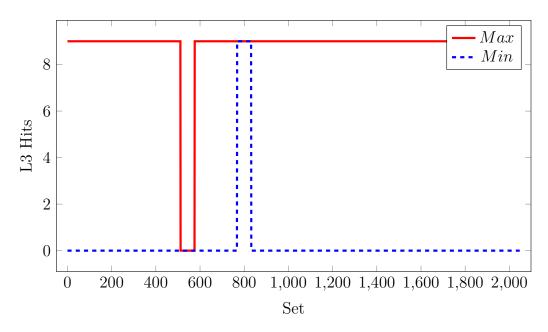

# 3.3.1 Pipeline of Intel Core CPUs